運(yùn)算放大器和比較器無(wú)論是外觀還是原理圖符號(hào)都差不多,如果把它上邊的標(biāo)識(shí)打磨掉的話很難區(qū)分開(kāi);二者在電子設(shè)計(jì)中都有著廣泛而重要的應(yīng)用,加之很多電路中會(huì)出現(xiàn)將運(yùn)放用作比較器的應(yīng)用,以至于有工程師朋友時(shí)不時(shí)的會(huì)將運(yùn)算放大器和比較器兩者混淆。

1、運(yùn)放原理簡(jiǎn)介

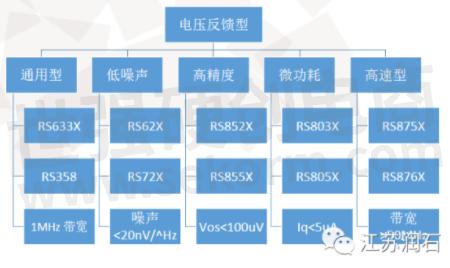

運(yùn)算放大器,是一種用于信號(hào)調(diào)理的模擬芯片。比如對(duì)信號(hào)作放大,濾波,求和等。常見(jiàn)的有電壓反饋型運(yùn)放和電流反饋型運(yùn)放。這里只介紹電壓反饋型運(yùn)放,繼續(xù)細(xì)分可以分為下圖所示。如果按照制造的工藝來(lái)區(qū)分,可以分為Bipolar(三極管)工藝,CMOS工藝,JFET工藝。目前的低壓運(yùn)放主要是以CMOS工藝為主,因?yàn)槠溆休斎肫秒娏餍。C合性能優(yōu)異等優(yōu)勢(shì)。從應(yīng)用的角度來(lái)看,分為低壓供電和高壓供電,低壓供電為5V以內(nèi),高壓供電為5V以上,一般有24V耐壓,36V耐壓等級(jí)。

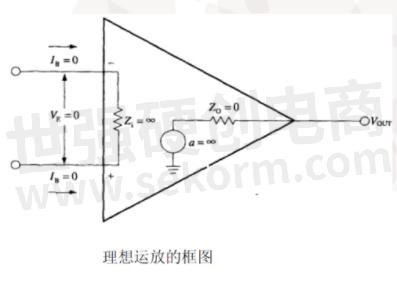

標(biāo)準(zhǔn)運(yùn)放的符號(hào)如圖所示,一個(gè)同相輸入端,一個(gè)反相輸入端,一個(gè)輸出端,一個(gè)正電源引腳,一個(gè)負(fù)電源引腳。所以運(yùn)放是差分輸入,單端輸出的(全差分運(yùn)放除外)。運(yùn)放本身并沒(méi)有參考點(diǎn),所以為了能夠正常工作,外面的電路需要給運(yùn)放一個(gè)穩(wěn)定的參考點(diǎn)。

1、運(yùn)放原理簡(jiǎn)介﹣-(續(xù))

運(yùn)放會(huì)放大其兩個(gè)輸入端的電壓差,輸出電壓等于運(yùn)放的開(kāi)環(huán)增益乘以輸入電壓差,而運(yùn)放自身的直流開(kāi)環(huán)放大倍數(shù)至少有80dB(一萬(wàn)倍)以上,因此只要輸入端電壓有 uV 級(jí)別的壓差,輸出就會(huì)有很大的電壓。當(dāng)然這種開(kāi)環(huán)放大在實(shí)際中是不好用的,因?yàn)檫\(yùn)放的開(kāi)環(huán)增益會(huì)隨溫度,負(fù)載,輸入電壓差大小而變化,為了得到穩(wěn)定的放大倍數(shù),在實(shí)際應(yīng)用中都是引入負(fù)反饋來(lái)維持穩(wěn)定的。

理想運(yùn)放的特點(diǎn):

①輸入電阻無(wú)窮大

②輸入失調(diào)電壓為零

③輸入偏置電流,失調(diào)電流為零

④開(kāi)環(huán)增益無(wú)窮大

⑤輸出阻抗為零

⑥帶寬無(wú)窮大

⑦壓援率無(wú)窮大

正是因?yàn)楝F(xiàn)實(shí)中不存在理想的運(yùn)放。才會(huì)們衍生出來(lái)各式各樣的的放大器,不同的應(yīng)用關(guān)注的指標(biāo)參數(shù)不一樣,總是需要強(qiáng)化某個(gè)指標(biāo),而弱化某個(gè)指標(biāo),選一個(gè)折中的來(lái)設(shè)計(jì)運(yùn)放。

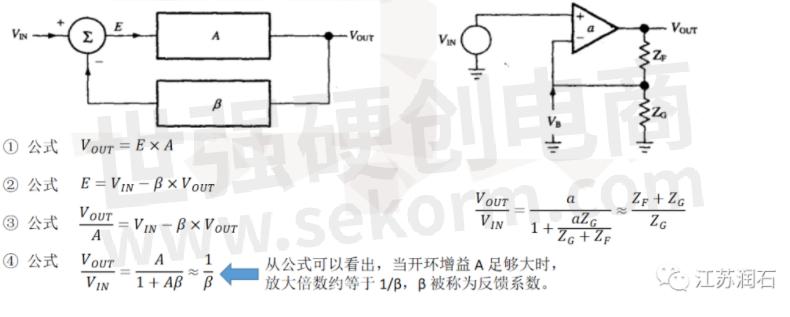

2、負(fù)反饋的本質(zhì)

為了穩(wěn)定的放大,需要引入負(fù)反饋。負(fù)反饋本質(zhì)上是利用輸出的一部分信號(hào)反饋到輸入,用運(yùn)放超高的開(kāi)環(huán)增益來(lái)修正許多因素導(dǎo)致的誤差。超高的開(kāi)環(huán)增益迫使輸入端的壓差保持在 uV 級(jí)別,也就是運(yùn)放輸入端虛短。 CMOs 運(yùn)放輸入偏置電流極小,運(yùn)放輸入端虛斷。

3、運(yùn)放的主要參數(shù):

①供電電壓范圍

②共模電壓輸入范圍(Vcm)

③輸入輸出軌到軌特性(Rail to Rail Input/output)

④帶寬增益積(GBW/GBP)

⑤壓擺率(SR)

⑥建立時(shí)間(Settingtime)與過(guò)驅(qū)動(dòng)恢復(fù)時(shí)間(Overload Recovery time)

⑦失調(diào)電壓(Vos)與溫漂(Vos/T)

⑧輸入偏置電流(IB)與失調(diào)電流(Ios)

⑨噪聲(Vnoise)

⑩開(kāi)環(huán)增益(Aol)

?共模抑制比(CMRR)

?電源抑制比(PSRR)

?輸入電容(Cin)

?靜態(tài)電流(Iq)

?全諧波失真加噪聲(THD+N)

?開(kāi)環(huán)輸出阻抗(Ro)與閉環(huán)輸出阻抗(Rout)

?相位裕度(φm)?

①供電電壓范圍

運(yùn)放自身沒(méi)有“地(GND)”的概念,標(biāo)準(zhǔn)運(yùn)放只有兩個(gè)電源引腳,正電源VCC和負(fù)電源VEE,因此運(yùn)放的供電電壓指的是VCC-VEE的差,習(xí)慣上把供電電壓范圍分為低壓(6v以內(nèi)),高壓(6V以上)。常見(jiàn)的高壓運(yùn)放耐壓等級(jí)一般有24V,36V。耐壓等級(jí)是跟選取的制造工藝有關(guān)系的

運(yùn)放有供電電壓范圍,意味著有最小值和最大值,供電電壓需要大于最小值,才能讓運(yùn)放正常工作。供電電壓不能超過(guò)最大值,否則運(yùn)放內(nèi)部會(huì)擊穿。

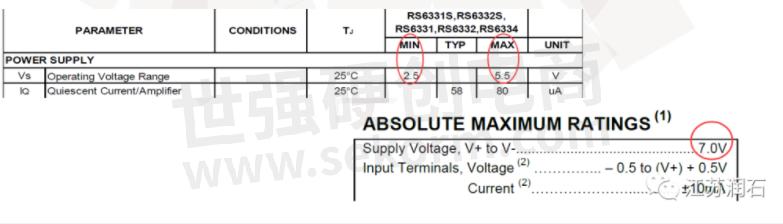

一般規(guī)格書會(huì)標(biāo)明兩個(gè)供電電壓值,建議值和極限值。建議值是廠家考慮了制造工藝的離散性,預(yù)留一定的余量。如下是潤(rùn)石通用系列運(yùn)放RS633X的規(guī)格書,建議值是2.5V~55V,實(shí)際上供電電壓位于2.2V~2.5V運(yùn)放都能工作,但是帶窗,噪聲,勒到勒輸出能力等參數(shù)都會(huì)惡化,因此最好是位干25V以上工作。55V~7V區(qū)間也能正常工作,但是大危險(xiǎn)了,供電電壓稍有波動(dòng)就可能燒掉運(yùn)放,因此廠家的建議最大值是5.5V。

②共模電壓輸入范圍(Vcm)

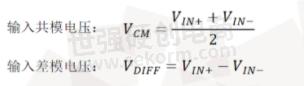

首先要理解什么是共模電壓,什么是差模電壓。對(duì)于運(yùn)放的同相輸入端(vin+)和反相輸入端(Vin-)來(lái)說(shuō):

輸入共模電壓定義了一個(gè)允許的輸入范圍,超出這個(gè)范圍后,會(huì)引起運(yùn)放輸入級(jí)對(duì)管的異常,此時(shí)運(yùn)放將不能線性的工作。RS633X的輸入共模電壓范圍如下表所示。

![]()

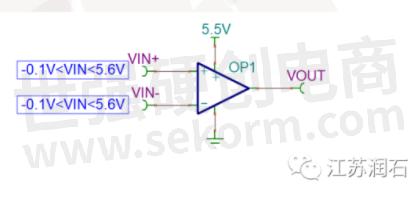

通俗來(lái)說(shuō),規(guī)格書里面給出的輸入共模電壓范圍,還有輸入差模電壓范圍,目的只有一個(gè),就是保證加在 VIN+ 和 VIN-上的電壓不能超過(guò)允許的電壓范圍。對(duì)于RS633X來(lái)說(shuō),輸入電壓的范圍只允許在VSS-0.1V~VCC+0.1V之內(nèi),如果供電電壓是5.5V,那么輸入允許的電壓范圍就是-0.1V~5.6V。

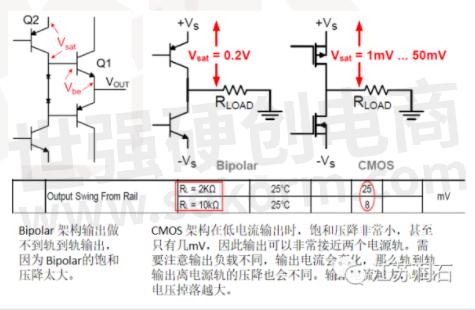

③輸入輸出軌到軌特性(Rail to Rail Input/output)

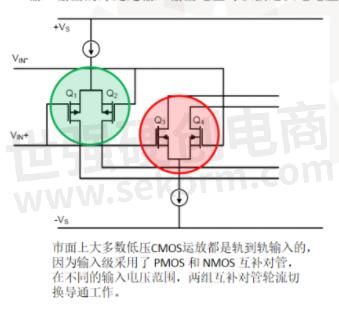

“軌”是指電源軌,包括正電源軌和負(fù)電源軌,如果負(fù)電源軌是接地,那么負(fù)軌就是地(GND),正軌就是VCC。傳統(tǒng)的Bipolar(三極管)工藝JFET工藝,都做不到軌到軌輸入。CMOS工藝在輸入級(jí)用一對(duì)PMOS和一對(duì)NMOS組成互補(bǔ)輸入,可以做到軌到軌輸入。軌到軌輸出是指輸出端的電樂(lè)可以接近正軌和負(fù)軌,注意是接近,不是等于。軌到軌輸入輸出的好處是輸入輸出電壓可以接近供電電壓,這樣在低供電電壓時(shí)輸入輸出的動(dòng)態(tài)范圍可以做得最大化。

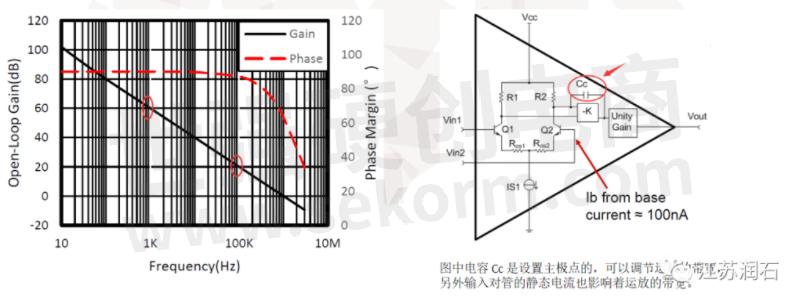

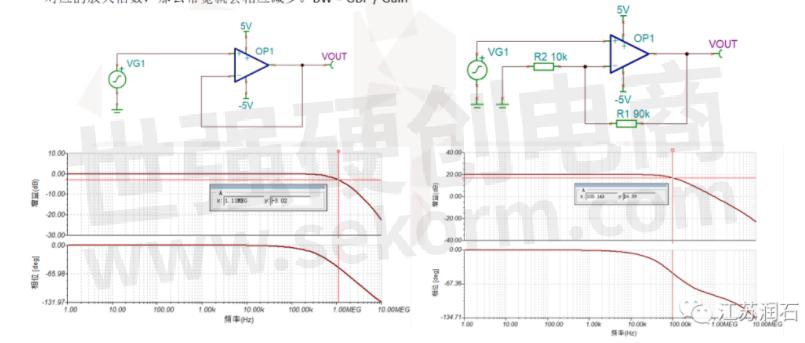

④帶寬增益積(GBW/GBP)

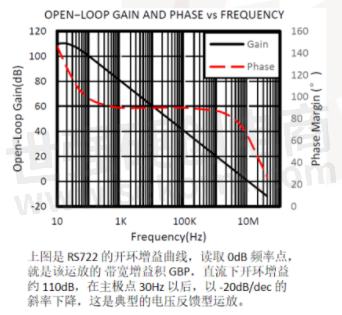

對(duì)于電壓反饋型運(yùn)放來(lái)說(shuō),有帶寬增益積的概念,因?yàn)橛^察電壓反饋型運(yùn)放的開(kāi)環(huán)增益曲線,從主極點(diǎn)以后,帶寬和增益的乘積幾乎是一個(gè)常數(shù)。對(duì)于電流反饋型運(yùn)放來(lái)說(shuō),這個(gè)是不成立的。

通常用開(kāi)環(huán)增益曲線與0 dB相交處為帶寬增益積,(有時(shí)候高帶寬的運(yùn)放并不成立)。下圖是RS633X的開(kāi)環(huán)增益曲線,可以看到,0dB相交處,約為11MHz,表示該器件在單位增益同相放大時(shí),帶寬為11MHZ。

④帶寬增益積(GBW/GBP)---(續(xù))

對(duì)于不同的增益(需要用噪聲增益去計(jì)算),廠家規(guī)格書給出的帶寬增益積一般都是單位增益時(shí)的帶寬,如果電路有對(duì)應(yīng)的放大倍數(shù),那么帶寬就會(huì)相應(yīng)減少。BW=GBP/Gain

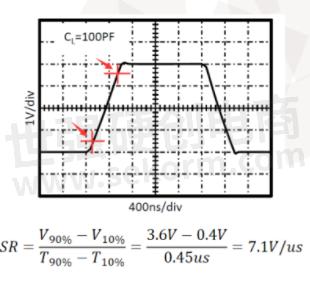

⑤壓擺率(SR)

壓擺率,Slew Rate,是描述運(yùn)放對(duì)于大信號(hào)邊沿響應(yīng)的快慢。從下面的波形中可以看出具體的定義。輸入共模電壓大小,溫度的高低,都會(huì)影響壓擺率SR的大小。實(shí)際應(yīng)用可用公式計(jì)算:SR=2πf*Vp

比如想在10kHz頻率下,保持正常的輸出幅度5Vp,那么SR=2*3.14*10000*5/1000000=0.314V/us。需要用0.314V/us以上壓擺率的運(yùn)放才可以。由此引申出運(yùn)放另外一個(gè)帶寬,全功率帶寬(FullPower Bandwidth),運(yùn)放的實(shí)際帶寬由全功率帶寬和小信號(hào)帶寬中的最小值來(lái)決定。?

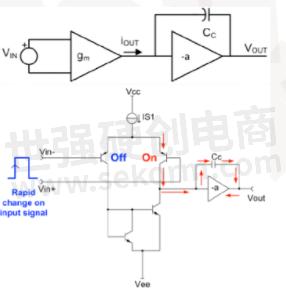

從運(yùn)放內(nèi)部看,對(duì)主極點(diǎn)電容Cc充放電的電流大小決定了壓擺巡的值。在小信號(hào)輸入時(shí)(通常100mVpp以內(nèi)),充放電的電流跟輸入信號(hào)的幅度是線性關(guān)系,此時(shí)輸出信號(hào)上升和下降時(shí)間并不是用壓擺率SR來(lái)計(jì)算的,此時(shí)運(yùn)放的邊沿上下時(shí)間近似一階電路的響應(yīng)計(jì)算

![]()

實(shí)際上比用壓率 SR 來(lái)計(jì)算快得多。當(dāng)輸入信號(hào)為大信號(hào)時(shí),充放電電流增大以至于被限制在最大值,類似于一個(gè)電容被恒流充電,那么電容的輸出電壓就是呈線性上升,此時(shí)上升下降時(shí)間要用壓擺率 SR 來(lái)計(jì)算。

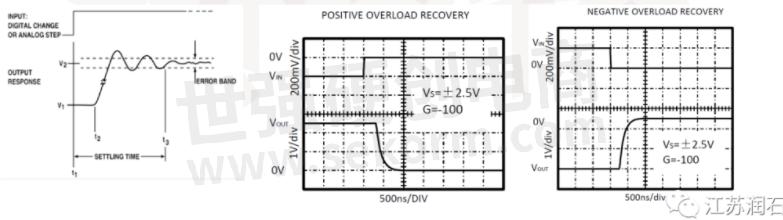

⑤建立時(shí)間(Setting time)與過(guò)驅(qū)動(dòng)恢復(fù)時(shí)間(Overload Recovery time)

建立時(shí)間,是運(yùn)放的階躍響應(yīng)輸出穩(wěn)定到一定精度所需要的時(shí)間。由于受到運(yùn)放小信號(hào)帶寬和壓擺率的限制,運(yùn)放的階躍響應(yīng)總是需要一定的時(shí)間,而且隨著相位裕度不同,輸出電壓的波動(dòng)也有很大差異。

對(duì)于小信號(hào)輸入(通常100mVpp以內(nèi)),輸出電壓的上升時(shí)間是Trise=0.35/f,然后再加上后段穩(wěn)定到需要精度的時(shí)間,就構(gòu)成了小信號(hào)輸入時(shí)的建立時(shí)間。對(duì)于大信號(hào)輸入,輸出電壓上升的時(shí)間用壓擺率計(jì)算,大信號(hào)輸出時(shí)一般沒(méi)有過(guò)沖振鈴,因此整個(gè)上升時(shí)間構(gòu)成了建立時(shí)間。建立時(shí)間主要受運(yùn)放主極點(diǎn)電容Cc充放電的值和相位裕度影響。

過(guò)驅(qū)動(dòng)恢復(fù)時(shí)間,是指放大后的輸出電壓超過(guò)了電源的供電電壓,當(dāng)輸入信號(hào)跳變時(shí),輸出電壓延遲的響應(yīng)時(shí)間。該參數(shù)是受運(yùn)放內(nèi)部的輸出級(jí)影響,主要是輸出管退出飽和狀態(tài)的時(shí)間。

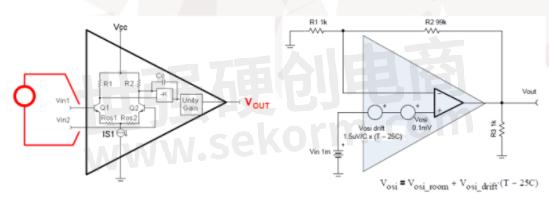

⑦失調(diào)電壓(Vos)與溫漂(ΔVos/AT)

理想運(yùn)放輸入電壓為零時(shí),輸出電壓也為零。實(shí)際上由于工藝的限制,運(yùn)放的輸入級(jí)做不到完全對(duì)稱,輸入失調(diào)電壓 Vos,是指為了讓運(yùn)放的輸出為零,需要額外在輸入端補(bǔ)償?shù)碾妷褐怠?/span>

CMOS運(yùn)放的失調(diào)電壓在5mV~10mV,出廠時(shí)可以經(jīng)過(guò)品員級(jí)的激光修調(diào)(Trim),失調(diào)電壓可以收窄到最大0.5mV,而封裝后的電子修調(diào),可以精確到50uV級(jí)別,如果需要更加小的失調(diào)電壓,運(yùn)放需要用自穩(wěn)零技術(shù),斬波和自穩(wěn)零技術(shù)可以把失調(diào)電壓控制在1uV級(jí)別。失調(diào)電壓在某個(gè)范圍時(shí)是有一定的條件的,比如規(guī)格書一般都是在共模電壓為一半VCC時(shí)測(cè)試的。實(shí)際應(yīng)用中,比如VCC=5V時(shí),當(dāng)共模電壓在0V~3.7V時(shí),輸入PMOS對(duì)管工作,失調(diào)電壓較小。當(dāng)共模電壓在3.7V~5V時(shí),輸入NMOS對(duì)管工作,NMOS對(duì)管一般不進(jìn)行修調(diào),此時(shí)失調(diào)電壓較大,達(dá)不到規(guī)格書的標(biāo)稱值。

溫漂是指運(yùn)放的失調(diào)電壓會(huì)隨溫度的變化而發(fā)生變化,Bipolar(三極管)工藝的運(yùn)放溫漂比較線性單調(diào),CMOS工藝的運(yùn)放溫漂不是線性單調(diào)的,但是為了方便描述,統(tǒng)一歸一化為X mV/℃。

運(yùn)放的失調(diào)電壓和溫漂會(huì)被線性放大, 左圖中,運(yùn)放的失調(diào)電壓Vos=0.1mV,溫漂為1.5uV/℃,電路配置放大100倍。

Vout

=(Vos+Vdirft X(T-25℃)x100?

失調(diào)電壓通常擁有正態(tài)分布的特性, 正常應(yīng)用時(shí)一般取最大值計(jì)算。為了減少 失調(diào)電壓和溫漂帶來(lái)的誤美。作直流放大時(shí),通常取最低輸入信號(hào)的十分之一來(lái)保持輸出電壓的精度。當(dāng)然,如果電路是作交流放大,那么失調(diào)電壓不會(huì)被放大,對(duì)輸出影響有限。

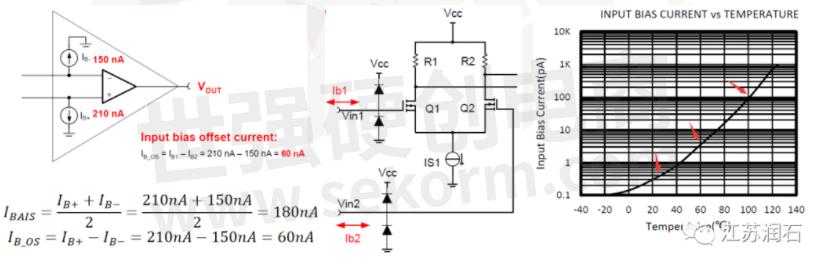

⑧輸入偏置電流(Ir)與失調(diào)電流(los)

理想運(yùn)放的輸入偏置電流和失調(diào)電流為零,早期使用Bipolar(三極管)工藝時(shí),由于三極管屬于電流控制型元件,運(yùn)放的兩個(gè)輸入端是三極管的基極,因此有偏置電流。CMOS屬于電壓控制型元件,其極電流為pA級(jí)別,基本上可以忽略不計(jì)。CMOS運(yùn)放輸入偏置電流和失調(diào)電流受溫度變化影響較大,常溫下幾乎為零,隨著溫度的上升,輸入偏置電流和失調(diào)電流指數(shù)增大,這是因?yàn)镃MOS運(yùn)放輸入引腳的ESD保護(hù)二極管漏電引起的,除非選用特別的制造工藝,否則超過(guò)100溫度下,輸入偏置電流都會(huì)增大成百上千倍。在一些高輸出內(nèi)阻的傳感器信號(hào)放大中,可能會(huì)引起額外問(wèn)題,如果放大電路外部使用的電阻是百kΩ級(jí)別,那么在運(yùn)放輸出端將會(huì)產(chǎn)生新的失調(diào)誤差。

⑨噪聲(Vnoise)

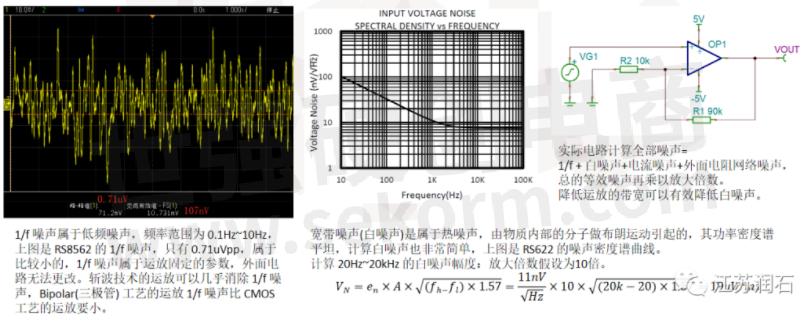

三極管,MOS管,電阻,都會(huì)產(chǎn)生噪聲。在運(yùn)放中,噪聲主要有兩種,低頻噪聲(1/f),寬帶噪聲(白噪聲)。在通用架構(gòu)的運(yùn)放中,存在電壓噪聲和電流噪聲,噪聲由于是一個(gè)隨機(jī)的信號(hào),為了方便描述,用其功率密度譜來(lái)衡量,這樣方便畫出噪聲功率密度譜與頻率的關(guān)系,最直觀的方式就是用Vpp值或者Vrms值描述,一般Vpp=6.6*Vrms。

⑩開(kāi)環(huán)增益(Aol)

運(yùn)放的開(kāi)環(huán)增益就是不加負(fù)反饋時(shí)的頻率響應(yīng)特性。運(yùn)放直流的開(kāi)環(huán)增益高達(dá)100dB(十萬(wàn)倍)以上,如此高的開(kāi)環(huán)增益,在實(shí)際上是不適合直接放大信號(hào)的,開(kāi)環(huán)增益直接受溫度、輸出負(fù)載,供電電壓輸入電壓幅度影響,而目會(huì)大幅度的波動(dòng),所以一定需要引入負(fù)反饋來(lái)提高閉環(huán)增益的穩(wěn)定性,單獨(dú)對(duì)比直流下的開(kāi)環(huán)增益意義不大。

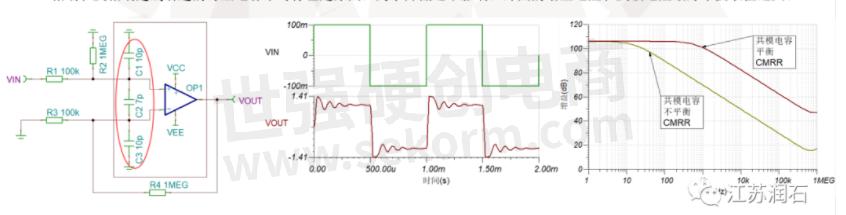

?共模抑制比(CMRR)

理想情況下,運(yùn)放只會(huì)放大其兩個(gè)輸入端的電壓差,對(duì)于共模電壓完全不響應(yīng)。共模抑制比描述的是運(yùn)放對(duì)輸入的共模電壓的抑制能力,輸出端以失調(diào)電壓的誤差形式表達(dá),一種簡(jiǎn)單的測(cè)量方式是在輸入端加一個(gè)固定的共模電壓,測(cè)量運(yùn)放輸出的偏移量,來(lái)計(jì)算共模抑制比。

實(shí)際運(yùn)放對(duì)共模信號(hào)無(wú)法完全抑制,是由于運(yùn)放輸入對(duì)管在工藝上沒(méi)辦法做到完全對(duì)稱,包括輸入對(duì)管的跨導(dǎo)增益,寄生電容,溫度系數(shù)等。而且共模抑制比是頻率的函數(shù),頻率越高,共模抑制比越低。

為了提高差分放大電路的共模抑制比,就要求左圖四個(gè)電的匹配度要非常高,如果電阻的精度是1%,那么直流下的共模抑制比只有46dB。為了解決這個(gè)問(wèn)題,芯片廠家專門生產(chǎn)了包含四個(gè)高精度電阻的差分運(yùn)放,這樣直流下的共模抑制比可以高達(dá)100dB。在電路設(shè)計(jì)上,同相放大器電路,兩個(gè)輸入端的電壓跟隨輸入信號(hào),會(huì)由于其模抑制比的原因而在輸出端產(chǎn)生額外失調(diào)電壓。對(duì)于高精度的ADC采樣,可能會(huì)影響后幾bit讀數(shù)。反相放大器電路,其同相端一般接到古定的參考電壓上,運(yùn)放兩個(gè)輸入端的電壓比較恒定,因此在輸出端產(chǎn)生的失調(diào)電壓相對(duì)較低。

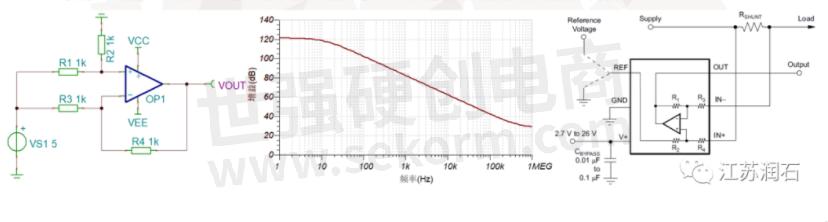

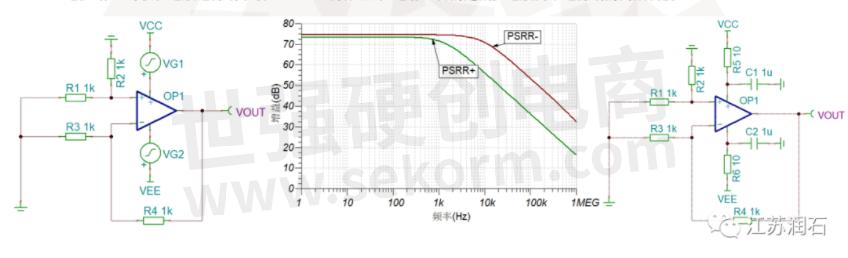

?電源抑制比(PSRR)

運(yùn)放的電源電壓波動(dòng)時(shí),會(huì)輕微影響內(nèi)部的恒流源靜態(tài)點(diǎn),導(dǎo)致運(yùn)放輸出端以失調(diào)電壓的形式出現(xiàn)誤差。電源抑制比描述的是運(yùn)放對(duì)電源波動(dòng)的抑制能力,通常分為對(duì)正電源軌PSRR+,負(fù)電源軌PSRR-的抑制能力,兩者通常有點(diǎn)差異。電源抑制比也是頻率的函數(shù),頻率越高,電源抑制比PSRR越低。

電源抑制比的測(cè)量如左圖所示,通過(guò)測(cè)量運(yùn)放輸出端的殘余信號(hào)來(lái)計(jì)算。從右圖PSRR曲線可以看出,低頻下都有很好的抑制能力,當(dāng)頻率逐漸升高時(shí),開(kāi)始以-20dB/dec下降,這是因?yàn)檫\(yùn)放內(nèi)部差分對(duì)的拖尾恒流源的電容隨頻率改變,恒流源的等效阻抗隨頻率升高而減少。所以如果應(yīng)用中的負(fù)電源VEE由DC-DC或者電荷泵等器件產(chǎn)生,那么需要做好濾波工作,可以在運(yùn)放電源端串聯(lián)RC,LC,或者磁珠+電容,目的是減少運(yùn)放兩個(gè)電源端的高頻紋波。

?輸入電容(Cin)

運(yùn)放的輸入電容分為共模輸入電容和差模輸入電容,現(xiàn)在的CMOS運(yùn)放大多數(shù)具有EMI抑制功能,其共模輸入電容和差模輸入電容會(huì)偏大一點(diǎn),大概有10pF~20pF。運(yùn)放的輸入電容在某些應(yīng)用下會(huì)引起問(wèn)題,主要有引起輸出振蕩,或者由于兩個(gè)輸入端的共模電容偏差較大,引起共模抑制比惡化。

反相端的輸入共模電容會(huì)與反饋電阻RF形成一個(gè)極點(diǎn),從輸出端反饋回來(lái)的信號(hào)會(huì)有相移,再回饋到反相端,造成同相端和反相端的相移不是正常的對(duì)應(yīng)狀態(tài),輸出電壓會(huì)存在過(guò)沖或者直接振蕩。要解決此問(wèn)題,一個(gè)是需要等比例整體降低反饋電阻的阻值,另一個(gè)是在反饋電RF上并聯(lián)電容,引入額外的零點(diǎn)來(lái)修正造成的相移。

共模輸入電容如果不對(duì)稱平衡,會(huì)引起共模抑制比的惡化,因?yàn)檫\(yùn)放同相端和反相端的相移不相等,自然進(jìn)入運(yùn)放的信號(hào)就不是對(duì)稱的,此時(shí)共模信號(hào)也會(huì)被放大。除了運(yùn)放自身引腳以及內(nèi)部電路引起的不平衡以外,PCB Layout時(shí),同相端和反相端走線引起的寄生電容不對(duì)稱也是原因,為了降低這個(gè)影響,外圍的增益電阻和反饋電阻最好不要取值過(guò)大。

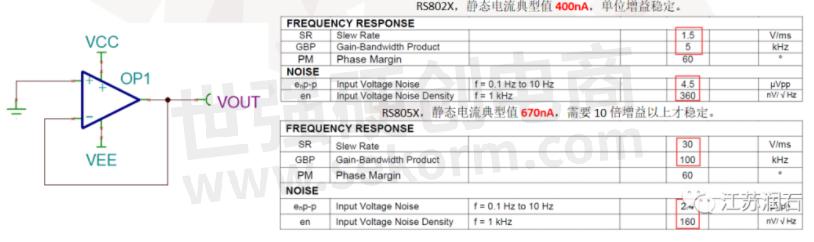

?靜態(tài)電流(Iq)

運(yùn)放的靜態(tài)申流是指運(yùn)放外干放大狀態(tài),并目其輸入共模電壓外干某個(gè)電壓,器件自身消耗的電流,輸出負(fù)載的電流是不計(jì)算在內(nèi)的。因?yàn)闃?biāo)準(zhǔn)的運(yùn)放沒(méi)有接地引腳,所以流入VCC引腳的電流約等于流出VEE引腳的電流。運(yùn)放生產(chǎn)商測(cè)試運(yùn)放的靜態(tài)電流時(shí),采用下冬的電路,正負(fù)電源供電,配置成緩沖器,同相端接地,相當(dāng)于輸入共模電壓是運(yùn)放供電電壓的一半,然后測(cè)試vcC和VEE引腳的電流,輸出引腳不能接入負(fù)載。

運(yùn)放的靜態(tài)電流是內(nèi)部眾多恒流源偏置電流的來(lái)源,包括輸入差分對(duì)管,輸出推挽對(duì)管等。靜態(tài)電流直接影響運(yùn)放眾多的參數(shù),比如帶,噪聲,壓擺率等。靜態(tài)申流越大,帶寬和壓擺率越高,噪聲更低。所以高速(GBP>100MHz)的運(yùn)放其靜態(tài)電流一般都是5mA/ch以上。對(duì)干現(xiàn)在很多10T設(shè)備的應(yīng)用,又希望靜態(tài)電流做的非常低,那么只能犧牲帶寬,用擺率,噪聲,相位裕度等指標(biāo),降低內(nèi)部恒流源的偏置電流,來(lái)降低運(yùn)放整體的靜態(tài)電流。

?全諧波失真加噪聲(THD+N)

全諧波失真加噪聲,計(jì)算公式為![]() 意思是一個(gè)信號(hào)經(jīng)過(guò)運(yùn)放后,統(tǒng)計(jì)其輸出端各次諧波失真幅度,再加上帶內(nèi)噪聲,最后得出一個(gè)有效值電壓,相對(duì)于基波信號(hào)的比值。

意思是一個(gè)信號(hào)經(jīng)過(guò)運(yùn)放后,統(tǒng)計(jì)其輸出端各次諧波失真幅度,再加上帶內(nèi)噪聲,最后得出一個(gè)有效值電壓,相對(duì)于基波信號(hào)的比值。

在音頻領(lǐng)域應(yīng)用中,THD+N非常重要,因?yàn)閿?shù)字音頻存儲(chǔ)用的位數(shù)一般為24bit或者32bit,稍有些許失真就能把后面的幾bit淹沒(méi)掉,不過(guò)人耳對(duì)于一個(gè)信號(hào)的失真,大概5%以上的失真才可能聽(tīng)得出來(lái)。

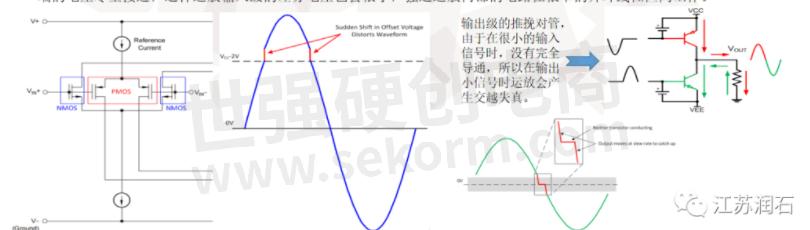

一個(gè)信號(hào)經(jīng)過(guò)運(yùn)放后產(chǎn)生失真的原因,分為輸入差分對(duì)管的交越失真,輸入阻抗非線性,密勒電容電流的非線性,輸出推挽級(jí)的交越失直。其中運(yùn)放的負(fù)反饋會(huì)盡最大能力去修正以上的失直,負(fù)反饋?zhàn)畲蟮淖饔茫褪亲屵\(yùn)放兩個(gè)輸入端的電壓盡量接近,這樣運(yùn)放輸入級(jí)的差分電壓也會(huì)很小,強(qiáng)迫運(yùn)放內(nèi)部的電路在很窄的開(kāi)環(huán)線性區(qū)間工作。

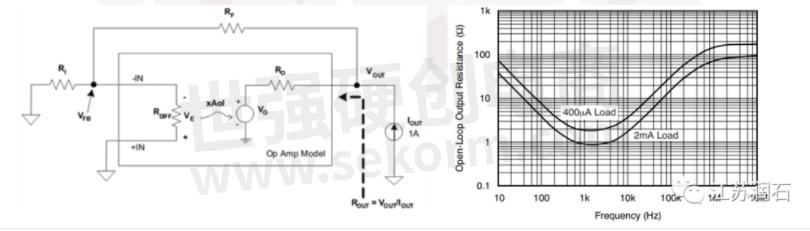

?開(kāi)環(huán)輸出阻抗(Ro)與閉環(huán)輸出阻抗(Rout)

開(kāi)環(huán)輸出阻抗Ro是運(yùn)放固有的特性,不隨運(yùn)放的增益而改變。閉環(huán)輸出阻抗Rout相當(dāng)于把整個(gè)運(yùn)放的電路看成一個(gè)黑匣子,計(jì)算的是運(yùn)放處于負(fù)反饋狀態(tài)下輸出端的阻抗。計(jì)算公式為![]() 。

。

Bipolar(三極管)工藝的運(yùn)放開(kāi)環(huán)輸出陽(yáng)抗比較平,到高頻段才非線性。CMOS工藝的運(yùn)放開(kāi)環(huán)輸出陽(yáng)抗則復(fù)雜得多。沒(méi)辦法用固定的曲線來(lái)衡量,不同帶寬,靜態(tài)電流的運(yùn)放開(kāi)環(huán)輸出阻抗差異很大。而且即使是同一個(gè)運(yùn)放,輸出負(fù)載吸取的直流電流不一樣,開(kāi)環(huán)輸出陰抗也不一樣,慶幸的是,運(yùn)放的負(fù)反饋會(huì)幫我們解決這些問(wèn)題。

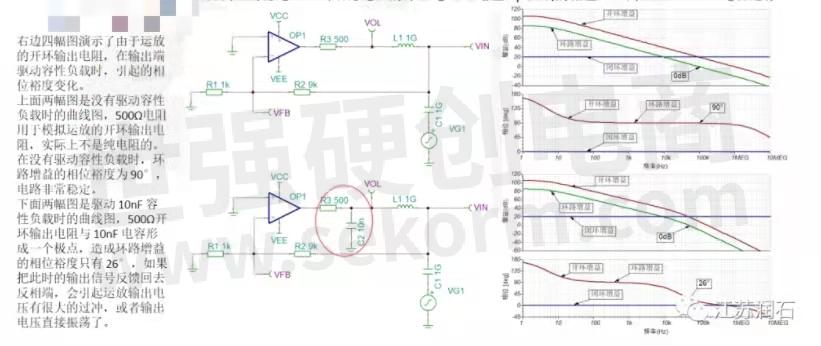

運(yùn)放的開(kāi)環(huán)輸出阻抗最大的危害,就是如果運(yùn)放輸出端存在容性價(jià)截,那么一老就會(huì)在開(kāi)環(huán)曲線上形成一個(gè)極占,如果極點(diǎn)在有用的頻帶內(nèi),相移會(huì)比較大,經(jīng)過(guò)反相端反饋回來(lái)后,會(huì)造成運(yùn)放振蕩。所以CMOS工藝的運(yùn)放,其輸出端不要輕易直接用電容接地濾波,即使要對(duì)輸出電壓濾波,也要先串聯(lián)一個(gè)電阻才能接電容到地。

?相位裕度(φm)

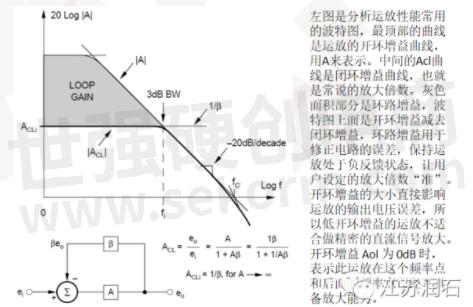

首先要了解運(yùn)放處于負(fù)反饋狀態(tài)下,增益跟頻率的三條曲線,開(kāi)環(huán)增益Aol,閉環(huán)增益1/β,環(huán)路增益Aol*β,簡(jiǎn)寫Aβ。因?yàn)檫@三條曲線決定了運(yùn)放負(fù)反饋的穩(wěn)定性,判斷穩(wěn)定性的標(biāo)準(zhǔn)是環(huán)路增益AB曲線的相位,距離相移180°,是否還存在45°的相位裕度。

4、運(yùn)放應(yīng)用的問(wèn)題探討

a)運(yùn)放最大能夠放大多少倍??

b)運(yùn)放可以放大多微弱的信號(hào)?

c)雙電源供電的運(yùn)放是否可以改成單電源供電?是否可以不對(duì)稱供電??

d)運(yùn)放的輸出總誤差是什么?

4、運(yùn)放應(yīng)用的問(wèn)題探討---(續(xù))

a)運(yùn)放最大能夠放大多少倍?

根據(jù)開(kāi)環(huán)增益的曲線以及增益帶寬積GBP的定義,Gain=GBP/Bandwidth,因此最大能夠放大多少倍是跟帶寬相關(guān)的,極限情況下放大超低頻信號(hào)(比如0.1Hz),那么放大倍數(shù)可以接近Aol 曲線低頻段增益,但是由于沒(méi)有足夠環(huán)路增益用于修正誤差,此時(shí)輸出電壓將偏離理想的輸出電壓值,而目單級(jí)過(guò)高的放大倍數(shù)會(huì)把運(yùn)放的失調(diào)電壓。噪聲放大,使電路“不好用”。建議單級(jí)放大電路控制在100倍以內(nèi)。

b)運(yùn)放可以放大多微弱的信號(hào)?

取決于所用運(yùn)放的底噪水平。如果需要運(yùn)放放大微弱信號(hào)(1uV~10mV),首先要讓運(yùn)放的輸入共模電壓遠(yuǎn)離兩個(gè)電源軌,保證能夠線性放大然后限制運(yùn)放的帶寬,這樣能有效降低帶外噪聲。總之,只要有用信號(hào)不被噪聲淹沒(méi),那么都能有效放大。

c)雙電源供電的運(yùn)放是否可以改成單電源供電?是否可以不對(duì)稱供電?

可以,標(biāo)準(zhǔn)運(yùn)放并沒(méi)有地GND引腳,所以運(yùn)放并不知道“地GND”在哪里,運(yùn)放內(nèi)部的電路都是參考VEE引腳的,但是對(duì)于輸入的信號(hào)來(lái)說(shuō),因?yàn)檫\(yùn)放放大的是輸入的差分電壓,因此必然會(huì)有輸入信號(hào)的參考點(diǎn),外理好輸入共模電壓的范圍即可,負(fù)反饋的存在可以不對(duì)稱供電。

d)運(yùn)放的輸出總誤差是什么?

總共有9項(xiàng)誤差構(gòu)成, Verror=Vos+Vos_drift+Vbias+Vbias_drift+Vnoise +VCMRR+VPSRR+VAOI+VEMIRR?

不管是直流放大還是交流放大,實(shí)際的輸出電壓跟理想的輸出電壓值之間的差距。就是以上9項(xiàng)誤差構(gòu)成的,而目運(yùn)放的這些誤差項(xiàng)。都是在一直變化的,隨溫度變,隨時(shí)間變。引入負(fù)反饋非常重要,能夠無(wú)時(shí)無(wú)刻地修正以上誤差,當(dāng)然不是“消除”,而是盡量減少。

5、運(yùn)放與比較器的區(qū)別

運(yùn)放的設(shè)計(jì)目的是用于存在負(fù)反饋的場(chǎng)合,比較器是用于開(kāi)環(huán)應(yīng)用。

a)為了負(fù)反饋穩(wěn)定,運(yùn)放內(nèi)部有密勒電容,比較器則不需要,因此比較器沒(méi)有壓擺率這個(gè)參數(shù)。輸入一個(gè)階躍信號(hào)時(shí),運(yùn)放上升是慢吞吞的。而比較器則馬上就翻轉(zhuǎn)了。

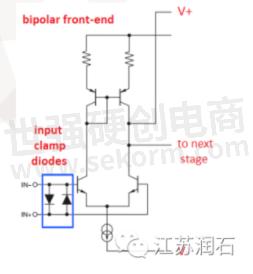

b)一些高壓的運(yùn)放,還有Bioolar(三極管)工藝的運(yùn)放,兩個(gè)輸入引腳之間會(huì)存在雙向鉗位二極管。低壓的CMOS運(yùn)放一般沒(méi)有,比較器沒(méi)有雙向鉗位的二極管。所以把運(yùn)放當(dāng)比較器來(lái)用,要判斷是否需要加限流電阻,以免燒掉運(yùn)放。

c)運(yùn)放有帶寬,比較器一般不用帶寬來(lái)衡量其翻轉(zhuǎn)速度,用TPHL,TPLH,Tfall,Trise,來(lái)表示速度。

一個(gè)簡(jiǎn)單的計(jì)算比較器速度方法是

d)運(yùn)放輸出端都是推挽輸出的,比較器可以做成推挽輸出,也可以做成開(kāi)漏輸出。

e)運(yùn)放輸出過(guò)載后,需要比較長(zhǎng)的恢復(fù)時(shí)間。比較器的過(guò)載恢復(fù)時(shí)間非常短。?

f)有些運(yùn)放的輸入共模電壓范圍,不能到正電源軌。許多比較器是支持到正電源軌的。?

g)運(yùn)放可以當(dāng)比較器使用(在一些低速翻轉(zhuǎn)場(chǎng)合可以),而比較器不能當(dāng)運(yùn)放使用。

6、如何根據(jù)應(yīng)用選擇合適運(yùn)放

運(yùn)放選擇判斷步驟:

1、實(shí)際工作電壓,選用低壓運(yùn)放還是高壓運(yùn)放,高壓運(yùn)放比低壓運(yùn)放貴很多:

2、是否需要軌到軌輸入/輸出特性:

3、客戶具體的應(yīng)用場(chǎng)合,比如:

1)音頻應(yīng)用,注重帶寬,壓擺率,噪聲,輸出軌到軌特性

2)便攜式產(chǎn)品應(yīng)用,注重靜態(tài)電流,帶寬等:

3)傳感器應(yīng)用,注重失調(diào)電壓,溫漂,靜態(tài)電流,輸入偏置電流,共模抑制比等;

4)采樣電流應(yīng)用,注重帶寬,失調(diào)電壓,溫漂,靜態(tài)電流等:

5)濾波器應(yīng)用,注重帶寬,樂(lè)擺率,軌到軌輸入輸出特性等:

6)儀器儀表應(yīng)用,注重失調(diào)電壓,溫漂,1/f噪聲等:

7)醫(yī)療應(yīng)用,注重噪聲,帶寬,軌到軌輸入輸出特性等。

7、潤(rùn)石公司運(yùn)放和比較器的優(yōu)勢(shì)

運(yùn)放:

全系列運(yùn)放種類齊全,低噪聲,高精度,高速,微功耗,通用型

有1μA/ch的微功耗運(yùn)放,適合用于PIR,氣體傳感器等應(yīng)用場(chǎng)合

通用系列運(yùn)放有失調(diào)電壓最大為0.5mV的版本

精密運(yùn)放失調(diào)電壓最大為5μV,溫漂最大50nV/℃,比同行最大20nV要好

高壓通用型運(yùn)放,高壓高精度型運(yùn)放,高壓差分運(yùn)放,儀表放大器 即將發(fā)布。

比較器:

全系列比較器種類齊全,微功耗,通用型,高速型

有1μA/ch的微功耗比較器,適用于智能家居等超低功耗產(chǎn)品

RS331/RS393/RS339,通用型1路/2路/4路比較器,支持軌到軌輸入進(jìn)行比較。

2022-06-23

2022-06-23